4.3 Latches

|

Un latch (Lat Memori Inglet) es un circuito electrónico usado para almacenar información en sistemas lógicos asíncronos. Un latch puede almacenar un bit de información. Los latches se pueden agrupar, algunos de estos grupos tienen nombres especiales, como por ejemplo el 'latch quad' (que puede almacenar cuatro bits) y el 'latch octal' (ocho bits). Los latches pueden ser dispositivos biestables asíncronos que no tienen entrada de reloj y cambian el estado de salida solo en respuesta a datos de entrada, o bien biestables síncronos por nivel, que cuando tienen datos de entrada, cambian el estado de salida sólo si lo permite una entrada de reloj. RC LatchLos latches a diferencia de los conectores no necesitan una señal de reloj para su funcionamiento.

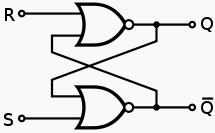

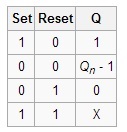

El latch lógico más simple es el RS, donde R y S permanecen en estado 'reset' y 'set'. El latch es construido mediante la interconexión retroalimentada de puertas lógicas NOR (negativo OR), o bien de puertas lógicas NAND (aunque en este caso la tabla de verdad tiene salida en lógica negativa para evitar la incongruencia de los datos). El bit almacenado está presente en la salida marcada como Q. Se pueden dar las siguientes combinaciones de entrada: set a 1 y reset a 0 (estado 'set'), en cuyo caso la salida Q pasa a valer 1; set a 0 y reset a 0 (estado 'hold'), que mantiene la salida que tuviera anteriormente el sistema; set a 0 y reset a 1 (estado 'reset'), en cuyo caso la salida Q pasa a valer 0; y finalmente set a 1 y reset a 1, que es un estado indeseado en los biestables de tipo RS, pues provoca oscilaciones que hacen imposible determinar el estado de salida Q. Esta situación indeseada se soluciona con los biestables tipo JK, donde se añade un nivel más de retroalimentación al circuito, logrando que dicha entrada haga conmutar a las salidas, denominándose estado de 'toggle'.

|