4.1 Modelos de Circuitos Secuenciales

|

Los circuitos considerados hasta aquí, tienen la característica de que su salida depende solamente de la combinación presente de valores de las entradas, es decir, a una misma combinación de entrada responden siempre con la misma salida. Debido a esto, estos circuitos se denominan combinacionales.

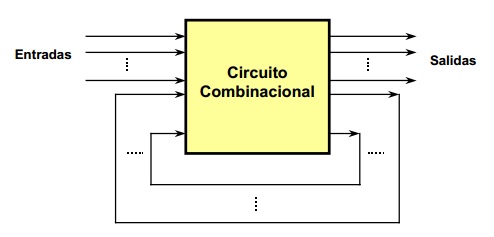

Circuito secuencial asíncrono En un circuito secuencial asíncrono, los cambios de estado ocurren al ritmo natural marcado por los retardos asociados a las compuertas lógicas utilizadas en su implementación, es decir, estos circuitos no usan elementos especiales de memoria, pues se sirven de los retardos propios (tiempos de propagación) de las compuertas lógicas usados en ellos. Esta manera de operar puede ocasionar algunos problemas de funcionamiento, ya que estos retardos naturales no están bajo el control del diseñador y además no son idénticos en cada compuerta lógica. Circuito secuencial síncrono Los circuitos secuenciales síncronos, sólo permiten un cambio de estado en los instantes marcados por una señal de sincronismo de tipo oscilatorio denominada reloj. Con ésto se pueden evitar los problemas que tienen los circuitos asíncronos originados por cambios de estado no uniformes en todo el circuito. Un circuito secuencial puede entenderse simplemente como un circuito combinacional en el cual las salidas dependen tanto de las entradas como de las salidas en instantes anteriores, esto implica una retroalimentación de las salidas como se muestra en diagrama de la siguiente figura:

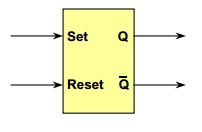

Multivibradores Biestables (Flip Flops). Los circuitos secuenciales básicos que funcionan también como unidades de memoria elementales se denominan multivibradores biestables (por tener dos estados estables –alto y bajo-), tambi´pen conocidos como Flip Flops. El Flip Flop Set Reset FF-SR

Diagrama de Bloques

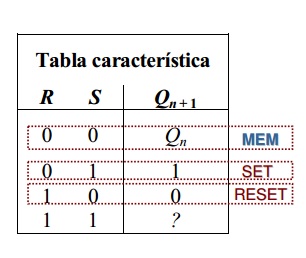

Tabla de Funcionamiento Los fabricantes de los circuitos integrados usan una tabla de funcionamiento para describir la operación de un circuito de una manera compacta, dicha tabla de funcionamiento no es otra cosa que una tabla de verdad como la usada para circuitos combinacionales, en la cual se ha introducido la información del tiempo que en el caso de circuitos secuenciales se vuelve esencial. Enseguida se ilustrará el uso de esta tabla para describir de manera compacta el funcionamiento del FF-SR.

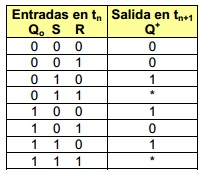

Como ejemplo introductorio, consideraremos el problema de diseñar el Flip Flop-SR. En este caso la salida Q+ depende del estado anterior Qo y de las entradas S y R, es decir:

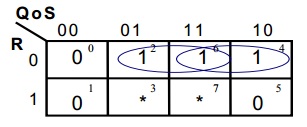

El Mapa de Karnaugh correspondiente es el siguiente:

De donde podemos obtener la expresión siguiente. (Aunque no es un procedimiento común, la experiencia a demostrado que se puede obtener una implementación más sencilla despreciando las condiciones sin cuidado), entonces:

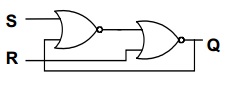

Para implementar con sólo compuertas NOR negamos dos veces la expresión para obtener:

Con lo cual podemos implementar el FF-SR con sólo dos compuertas NOR, como sigue:

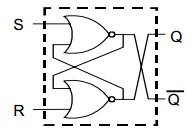

Esta implementación además tiene la ventaja de que también produce la función negada Q a la salida de la primera compuerta NOR, de manera que una mejor manera de dibujar este circuito es como se muestra en la siguiente figura:

|