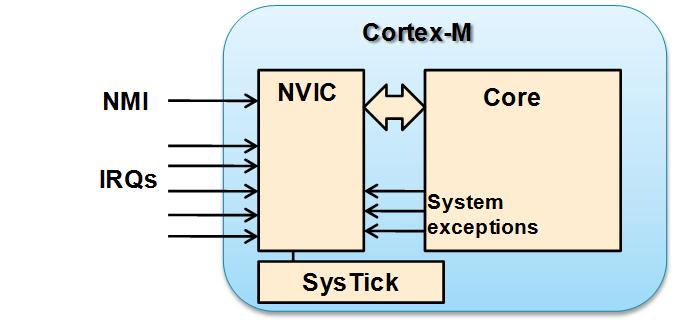

2.5 El NVIC y el Control de Interrupción (Nested Vectored Interrupt Controller)

|

Nested Vectored Controlador de Interrupciones (NVIC)

Dependiendo de la aplicación que utiliza el fabricante de silicio, el NVIC puede soportar hasta 240 interrupciones externas con hasta 256 niveles de prioridad diferentes que se pueden repriorizados dinámicamente. Es compatible con fuentes tanto nivel y de interrupción del pulso. El estado del procesador se guarda automáticamente por el hardware de entrada de interrupción y se restaura al salir de interrupción. El NVIC también apoya la cola en cadena de interrupciones. El uso de un NVIC en el Cortex-M3 significa que la tabla de vectores de Cortex-M3 es muy diferente a los anteriores núcleos ARM. La tabla de vectores de Cortex-M3 contiene la dirección de los manipuladores y ISR de excepción, no instrucciones como la mayoría de otros núcleos ARM hacen. El puntero de pila inicial y la dirección del manejador de reposición deben estar ubicados en 0x0 y 0x4 respectivamente. Estos valores se cargan en los registros de la CPU apropiadas en Reset.

Interrupt Controller (NVIC)Las interrupciones son utilizadas para minimizar los recursos del sistema, es decir, la aplicación está a la espera de que se produzca un determinado evento para interrumpir la misma y realizar una serie de funciones específicas. El controlador de interrupciones de la API proporciona un conjunto de funciones para trabajar con el Control vector de interrupción (CNTV). Las funciones se proporcionan para habilitar y deshabilitar las interrupciones, para el registro de los controladores de interrupción y para establecer su prioridad. Esta familia de Stellaris soporta treinta y dos fuentes de interrupción y tiene ocho niveles de prioridad. El CNTV está estrechamente unido con el microprocesador Cortex-M3. Cuando el procesador responde a una interrupción, el NVIC suministra directamente la dirección de la interrupción al procesador, por lo que se elimina la necesidad de un controlador de interrupciones global que consulte al controlador de interrupciones la causa de la misma y el desvió de esta hacia el controlador adecuado, ahorrando así, tiempo de respuesta del sistema. Todas las interrupciones por defecto tienen asignada la prioridad 0, que equivale a la máxima prioridad. Si se asigna el mismo nivel de prioridad a dos o más interrupciones, su prioridad será dada de forma hardware, es decir, según su posición en el vector de interrupciones. Por ejemplo, si el GPIO del Puerto A y B están configuradas con el mismo nivel de prioridad 1, entonces el GPIO del Puerto A será considerado como la de mayor prioridad. En el Stellaris LM3S8962 existen múltiples posibilidades de interrupciones, a través de los módulos GPIOs, de los módulos GPTMs, de los módulos UART, CAN, SSI, ADC, etc.

|